Research Interests:

- Quantum mechanical modeling of nanoscale devices.

- Device simulation of MOSFETs with ultrathin dielectrics.

- Solid-state physics study.

- Silicon heterostructure devices.

- MOS device modeling with strained silicon substrate.

Present Research Activities:

Currently I am working with Uniaxial Strained Silicon MOS Device Characteristics. Gate C-V characteristics and threshold voltage variation study is already been done. Impact of uniaxial <110> strain on double gate MOS devices is also revealed.

Publications:

M. Itrat B. Shams, Q. D. M. Khosru and A. Haque, "Impact of uniaxial strain on gate C-V characteristics of metal-oxide-semiconductor devices ," (Submitted in Journal of Applied Physics).

Md. Itrat Bin Shams, Md. Kawsar Alam and Quazi D. M. Khosru, "Effects of Uniaxial Strain on the Gate Capacitance of Double Gate MOSFETs," Proceedings of IEEE International Conference on Electron Devices and Solid-State Circuit 2008 (IEEE EDSSC), Hong Kong. Download

Md. Itrat Bin Shams, Quazi Deen Mohd Khosru and Anisul Haque,"Gate C-V Characteristics of Si MOSFETs with Uniaxial Strain Along <110> Direction," Proceedings of the International Conference on Electrical and Computer Engineering 2008 (ICECE), Dhaka, Bangladesh. Download

Research works Done:

Compact Modeling of Ultrathin MOS Devices

An improved compact gate capacitance-voltage (C-V) model for MOS devices with

An improved compact gate capacitance-voltage (C-V) model for MOS devices with

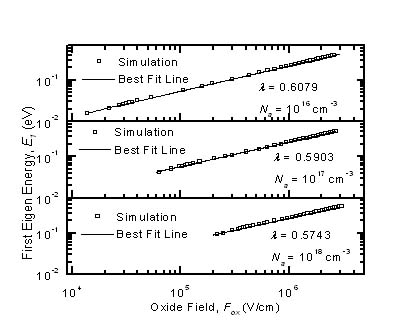

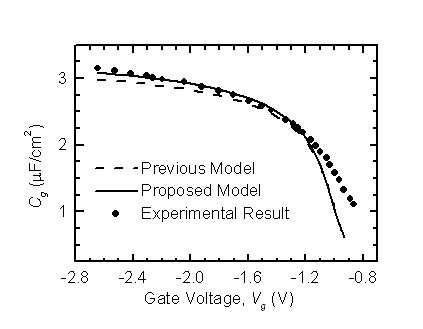

high-k gate dielectrics is proposed. In this model the effects of characteristics of dielectric material and substrate doping density are accurately included.Wave function penetration is considered to make the model robust for ultratjhin dielectrics. It is based on making λ the modified exponent of the 2/3 power law relationship (E1 α Fox^2/3 ) for the first eigenenergy, dependent on the characteristics of the dielectric material and on the substrate doping density. The effects of wave function penetration is included by extracting

λ from self-consistent solutions of coupled Schrödinger-Poisson equation for eigenenergies.

It is observed that λ strongly depends on barrier height and substrate doping density and other factors such as dielectric constant (k) of gate dielectric material, effective masses of holes and electrons, effective oxide thickness (EOT), work function of gate metal and existence of metal or polysilicon as gate, have negligible effect. An empirical relationship is proposed to represent λ as a function of barrier height and substrate doping density both for holes and electrons. It is found that λ increases with the increment in barrier height and λ decreases with the increment in doping density. Comparison with experimental C-V data shows that the proposed model is more accurate than existing model where λ was considered to be independent of characteristics of dielectric materials and doping densities.

It is observed that λ strongly depends on barrier height and substrate doping density and other factors such as dielectric constant (k) of gate dielectric material, effective masses of holes and electrons, effective oxide thickness (EOT), work function of gate metal and existence of metal or polysilicon as gate, have negligible effect. An empirical relationship is proposed to represent λ as a function of barrier height and substrate doping density both for holes and electrons. It is found that λ increases with the increment in barrier height and λ decreases with the increment in doping density. Comparison with experimental C-V data shows that the proposed model is more accurate than existing model where λ was considered to be independent of characteristics of dielectric materials and doping densities.

Publications:

M. Itrat B. Shams, K. M. Masum Habib, Q. D. M. Khosru, A. N. M. Zainuddin and A. Haque, "On the Physically Based Compact Gate C–V Model for Ultrathin Gate Dielectric MOS Devices Using the Modified Airy Function Approximation," IEEE transaction on Electron Devices, vol. 54, no. 9, September 2007. Download

Md. Itrat Bin Shams, K. M. Masum Habib, Rajib Mikail, Quazi Deen Mohd Khosru, A. N. M. Zainuddin and A. Haque,"An Improved Physically Based Compact C-V Model for Mos Devices with High-K Gate Dielectrics," Proceedings of the International Conference on Electrical and Computer Engineering 2006 (ICECE), Dhaka, Bangladesh. (Best Student Paper Award). Download

Md. Itrat Bin Shams, "Improved Compact Gate C-V Model for High-k gate Dielectrics Using Modified Airy Function Solution", Proceedings of the Student Paper Contest 2007, IEEE Electron Devices Society Bangladesh Chapter.

Signature Recognition:

An efficient technique is proposed for handwritten signature recognition. This technique is simple and it can detect skillful forgery. The exact area of forgery can also be evaluated. As the amount of data to be stored for each signature is less compared to other renowed algorithms, this method has a unique advantage.

Publication:

Md. Itrat Bin Shams, "Signature Recognition by Segmentation and Regular line Detection," Proceedings of the IEEE Tencon 2007, Taiwan. Download

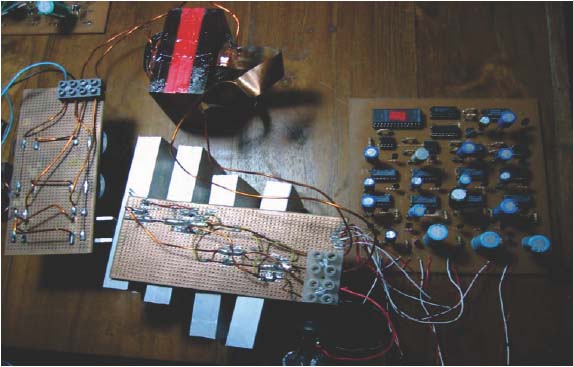

1kW Interactive Inverter System for

Unity PF Load

Renewable energy sources are becoming very popular all over the world as an alternate to the conventional one, made from natural resources (fossil fuels, etc.). So there is huge extent of works to be done in converting the variable DC voltage generated by sources like solar cells, etc. to a fixed DC and/or AC voltage. Our proposal of a utility interactive inverter system will prop up such works immensely. Here we have proposed a scheme, based on the use of conventional DCDC converter, followed by a PWM inverter, for generating an output waveform having low Distortion Factor (DF). A constant output voltage is assured by varying the modulation index of the PWM pattern, which is fed to the gate of the inverter. The output voltage is synchronized with the grid voltage by using Phase-Locked Loop (PLL). Standalone operation is performed by detecting the abnormal grid condition. The scheme is tested both for 110V (50Hz) and 240V

(60Hz) output. The efficiency is around 85% and hopefully it can be improved by identifying the

components, where the loss is incurring.

Renewable energy sources are becoming very popular all over the world as an alternate to the conventional one, made from natural resources (fossil fuels, etc.). So there is huge extent of works to be done in converting the variable DC voltage generated by sources like solar cells, etc. to a fixed DC and/or AC voltage. Our proposal of a utility interactive inverter system will prop up such works immensely. Here we have proposed a scheme, based on the use of conventional DCDC converter, followed by a PWM inverter, for generating an output waveform having low Distortion Factor (DF). A constant output voltage is assured by varying the modulation index of the PWM pattern, which is fed to the gate of the inverter. The output voltage is synchronized with the grid voltage by using Phase-Locked Loop (PLL). Standalone operation is performed by detecting the abnormal grid condition. The scheme is tested both for 110V (50Hz) and 240V

(60Hz) output. The efficiency is around 85% and hopefully it can be improved by identifying the

components, where the loss is incurring.

Report:

1kW Interactive Inverter System for Unity PF Load. Download